探索发现 · 交大智慧

探索发现 · 交大智慧

上海交大王国兴团队在高能效脉冲神经网络加速器芯片领域取得重要进展

近日,电子信息与电气工程学院微纳电子学系王国兴教授领衔的生物电路与系统实验室在高能效脉冲神经网络加速器芯片领域取得重要进展,相关成果以“A 0.67-to-5.4 TSOPs/W Spiking Neural Network Accelerator With 128/256 Reconfigurable Neurons and Asynchronous Fully Connected Synapses”(达到0.67-5.4 TSOPs/W能效,具有128/256个可重构神经元和异步全连接突触的脉冲神经网络加速器)为题在国际顶级期刊《IEEE固态电路期刊》(IEEE Journal of Solid-State Circuits,简称JSSC)上发表。

研究思路与方法

脉冲神经网络(SNN)加速器因其具有高计算能效的优势而得到了广泛关注。然而,不同使用场景对神经元模型的需求不同及基于事件驱动导致的不均匀脉冲分布,使对SNN芯片的吞吐量/面积的优化变得复杂,由此制约了芯片能效的提升。

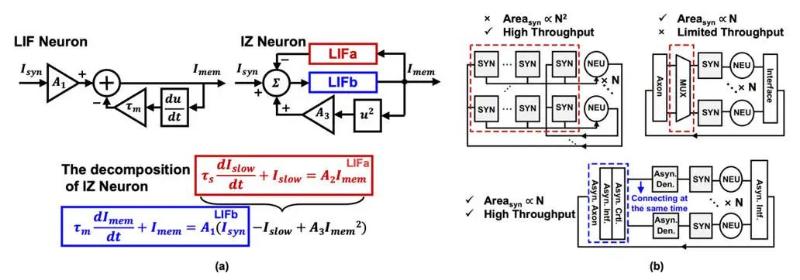

图1 脉冲神经网络加速器芯片中两项创新技术(a)可重构神经元技术(b)异步全连接突触技术

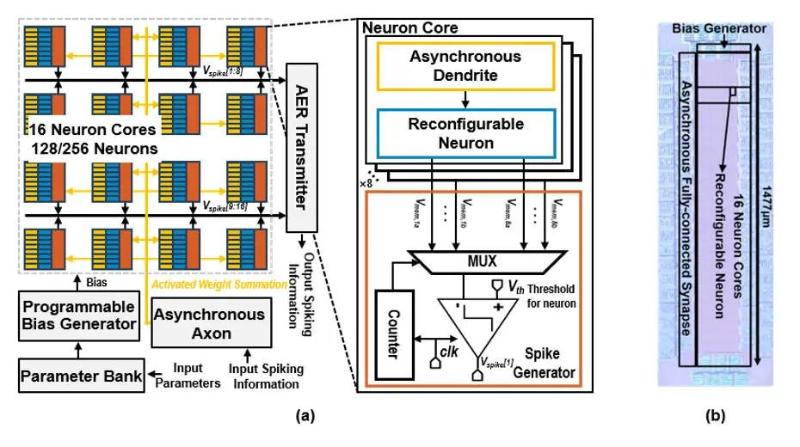

针对上述问题,研究团队开发出一种具有128/256个可重构神经元和异步全连接突触的SNN芯片。一方面,可重构神经元技术可根据实际应用需求将人工神经元电路在LIF模型和IZ模型之间无损切换,使加速器能效优势覆盖更多应用场景(图1a)。另一方面,亚阈值的异步全连接突触(图1b),为所有神经元在硅片上提供了类似人脑的并行全连接,突破了SNN加速器的能耗和单位吞吐率瓶颈。芯片整体架构如图2a 所示。

图2 脉冲神经网络加速器(SNN)芯片系统框图及显微照片

研究结果与意义

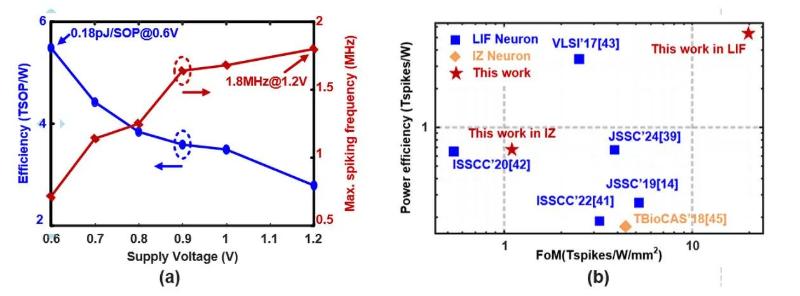

研究团队采用55纳米CMOS工艺完成了芯片原型开发(图2b)。所提出的芯片实现了5.37 TSOPs/W的峰值功率效率和25.6 MSOPs/s的吞吐量。神经元的近阈值操作与异步全连接突触相结合,针对图像特征提取应用的能量效率与已有工作相比降低9.42倍。芯片也展示了其高效的图像压缩编码、生物神经行为模拟等多种应用。

图3 芯片测试所得的能量效率、面积效率等性能指标

相关成果将推动SNN芯片应用于生物神经网络仿真、高能效类脑推理等场景,为人们在“研究脑”和“利用脑”两方面提供硬件助力。

论文信息

论文的第一作者为电院微纳电子学系博士生齐翔奡,通讯作者为其导师赵健副教授。

论文链接:https://ieeexplore.ieee.org/document/10546323

关于IEEE固态电路期刊

IEEE固态电路期刊(JSSC)是国际集成电路领域的旗舰期刊,旨在发布集成电路设计领域的最新、最好的技术成果。

近年来,上海交大电院微纳电子学系以探索国际前沿芯片设计技术为己任,先后在片上网络芯片、低功耗数模接口电路和高能效专用加速器等方面分别取得突破,成果陆续发表在JSSC上。