交大要闻

交大要闻

3金3银2铜+IEEE杯问鼎,上海交大学生团队在全国大学生集成电路创新创业大赛获佳绩

近日,第九届全国大学生集成电路创新创业大赛全国颁奖典礼在上海滴水湖会议中心举办,经过七大分赛区选拔,共662支来自全国161所高校的队伍晋级全国总决赛。经过激烈的角逐,上海交通大学集成电路学院(信息与电子工程学院)8支晋级队伍脱颖而出,斩获全国一等奖三项,二等奖三项,三等奖两项,其中刘继泽、田洁晨、任钊辉队伍捧杯,一举拿下IEEE杯赛企业大奖。

全国大学生集成电路创新创业大赛是国内集成电路领域最大规模高校赛事,中国高等教育学会全国高校竞赛榜单唯一入榜集成电路专业赛事。第九届全国大学生集成电路创新创业大赛于2025年1月启动,共分为4大赛道,11个技术方向,25个杯赛,覆盖集成电路全产业链,报名队伍超过7400支,参赛师生逾20000人,参与高校500余家。经过西南、华北、东北、华中、华东、华南、西北七大分赛区选拔,有来自161所高校的662队伍晋级全国总决赛。8月22日到8月23日,大赛总决赛各参赛团队在上海海洋大学进行答辩,经过为期两天的激烈角逐,共有134支队伍获得一等奖、200支队伍获得二等奖、313支队伍获得三等奖。

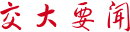

集成电路学院获奖情况

IEEE杯一等奖、企业大奖作品介绍

赛题:高速串行接口接收机模拟前端

队员:刘继泽、田洁晨、任钊辉

指导教师:金晶、过悦康

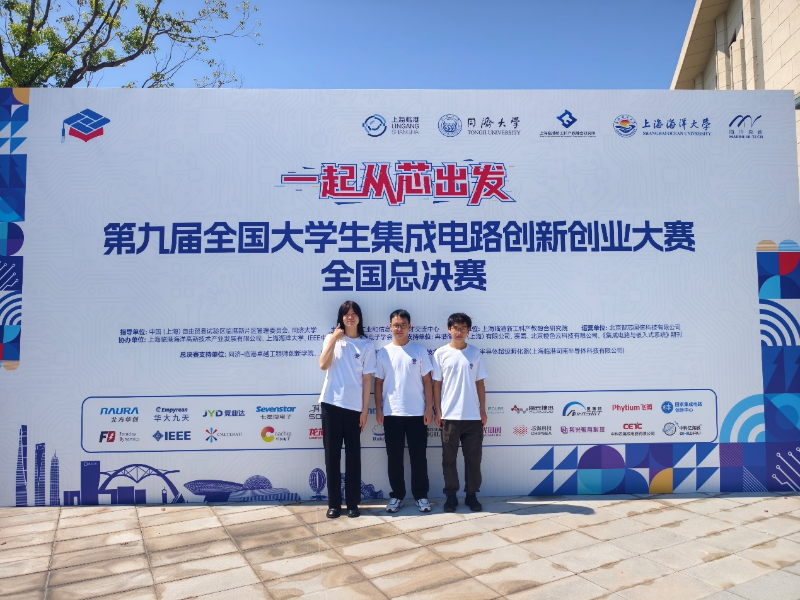

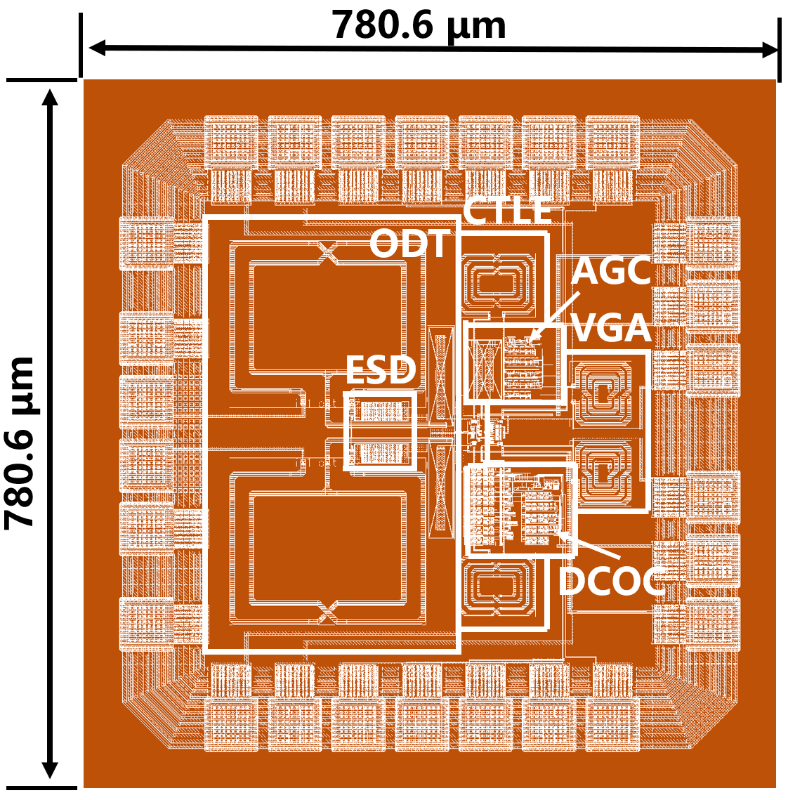

本项目设计并实现了一款应用于100 Gbps高速串行接口的模拟前端(AFE)接收机电路,基于65nm CMOS工艺,涵盖片上端接(ODT)、连续时间线性均衡器(CTLE)、可变增益放大器(VGA)、自动增益控制(AGC)及直流失调消除(DCOC)五大功能模块。

系统结构框架图

该设计实现了100 Gbps PAM4信号接收,具备1.0 Vp-p差分输入幅度支持、100 Ω差分端接、低输入电容等关键特性。CTLE提供2.79 dB至21.59 dB的可调均衡增益,VGA实现6.69 dB的增益调节能力,整体功耗低至7.17 mW,远低于设计目标20 mW。后仿真验证了设计的均衡性能与增益连续可调性,确保信号完整性。

系统电路版图

项目在性能与创新方面具有突出特点:1.采用T-coil结构优化寄生参数,提升带宽;2.引入共模/差模协同控制,改善线性度;3.通过电感峰化及可调元件实现多频段响应解耦,增强均衡能力;4.AGC与DCOC模块实现自动校准,提高系统稳定性。整体设计在低功耗、高速传输与信号调理等方面取得显著成果,为未来高速通信系统提供了可靠的模拟前端解决方案。

奕斯伟杯一等奖作品

介绍赛题:基于RISC-V架构在边缘侧的AI应用

队员:韩湘锐、张浩宇、韩汪洋

指导教师:何卫锋、孙亚男

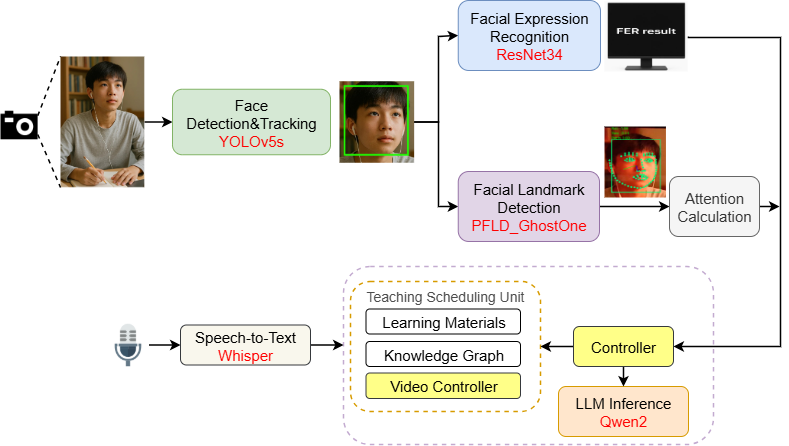

本作品面向教育数字化场景,针对现有智能教学系统“教学-反馈”链路分离的问题,构建了实时情感与专注度驱动的动态教学交互体系。系统依托搭载EIC7700X AI SoC的开发板,集成轻量化YOLOv5s人脸检测模型、ResNet34表情识别模型与PFLD_GhostOne面部关键点检测模型,结合Qwen2大模型推理引擎,基于Whisper语音识别增强多模态交互,实现从表情捕捉到面部关键点检测与专注度分析,再到动态教学策略生成的闭环响应。

系统工作流程图

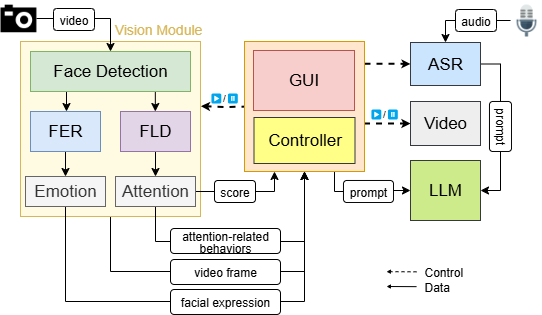

程序架构图

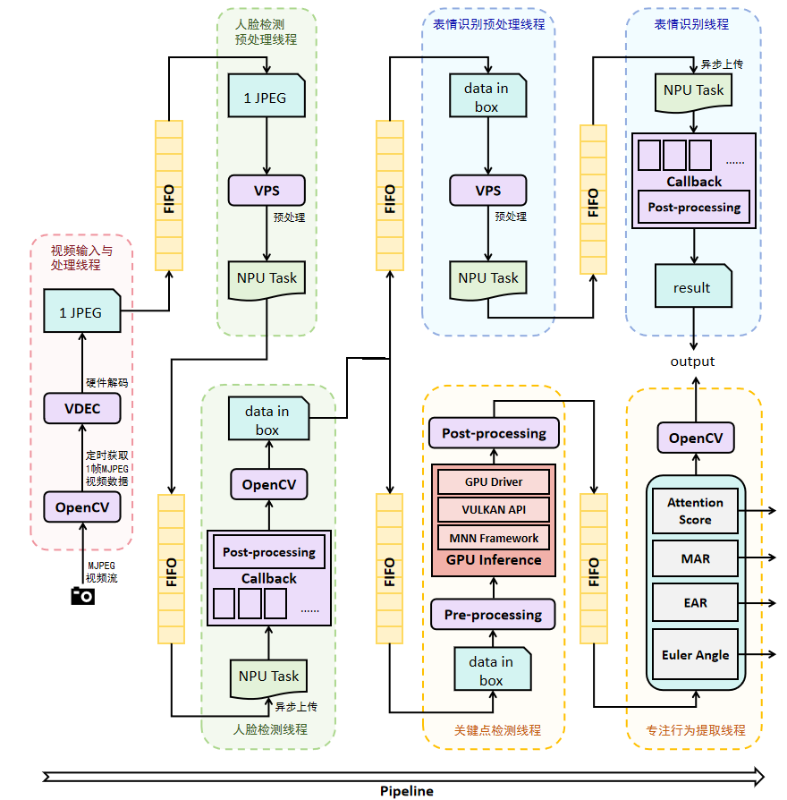

团队采用多线程流水处理的架构,实现多模型实时处理下的高吞吐率,并充分利用NPU、DSP、GPU、Video CoDec等片上硬件资源,对模型推理、后处理、视频解码与处理、界面渲染等过程加速。系统中的神经网络模型均实现了较好的性能表现和较低的推理延时,各处理过程在硬件加速下相比于CPU实现有较大的性能提升。

视觉模型推理流水线

作品创新性地将情感计算、专注度分析与边缘智能深度融合,更加多维度地评估学习状态,突破传统课后诊断模式,提出“感知即干预”的线上学习实时人机交互系统。通过硬件处理加速、异步推理优化,形成高鲁棒性嵌入式解决方案,全流程本地化部署在保证高精度的同时实现低延迟的端到端视频处理与模型推理,提供低功耗、高隐私安全AI赋能教育范式。

雨骤杯一等奖作品介绍

赛题:基于“雨珠系列片上仪器”构建自主可控MOSFET测试系统

队员:龙羿辰、陈奕扬、李宇乐

指导教师:王国兴

本项目实现了一个支持多模式、多器件切换的MOSFET测试、提参、建模、应用场景仿真的一体化平台,包含磁吸式负载板与控制程序。四通道批量测试:支持最多4片MOSFET芯片的批量测试;多模式测量:可控制切换为直流、交流、瞬态特性测量; 数字路由控制:利用雨珠的DIO功能控制继电器和模拟开关路由;电源反馈式调节:通过软件实现电源电压反馈调节,适应阻抗变化;板载放大电路:39倍增益运放,放大电流信号。

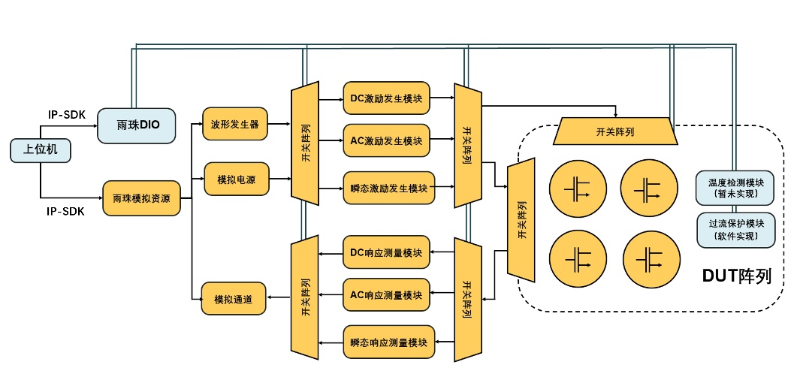

MOSFET测试平台系统框图

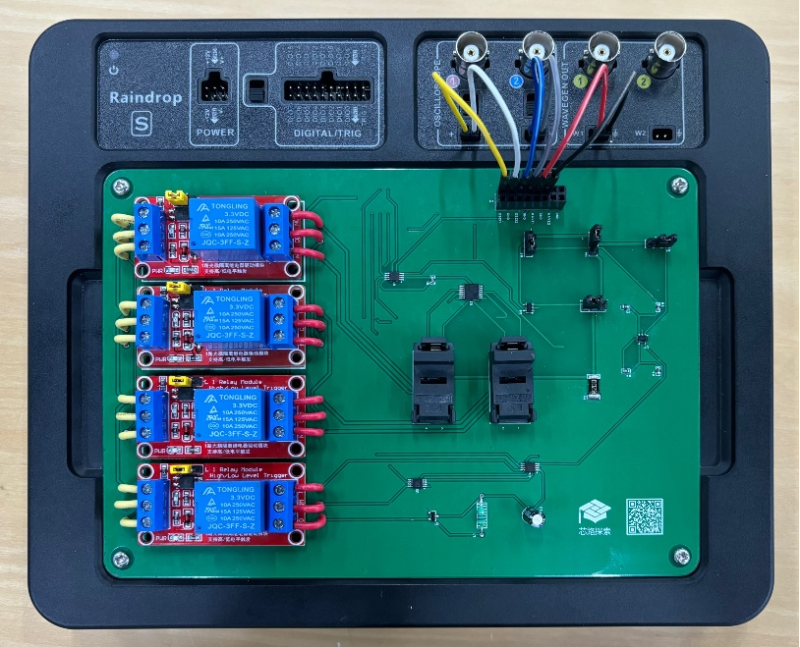

MOSFET测试平台实物图

针对分立MOSFET器件测试、建模与应用验证流程繁琐、技术门槛高的痛点,本项目设计并实现了一套集硬件测试、软件控制、智能建模与仿真验证于一体的“MOSFET一站式 EDA套件”。该软件套件由Navigator(项目管理器)、Measure(高精度测试平台)、Analyst(数据分析与智能建模)和Simplus(综合仿真器)四大核心组件构成。项目引入“大语言模型(LLM)+本地仿真验证”的闭环迭代式建模方法,显著降低了器件建模的技术壁垒。

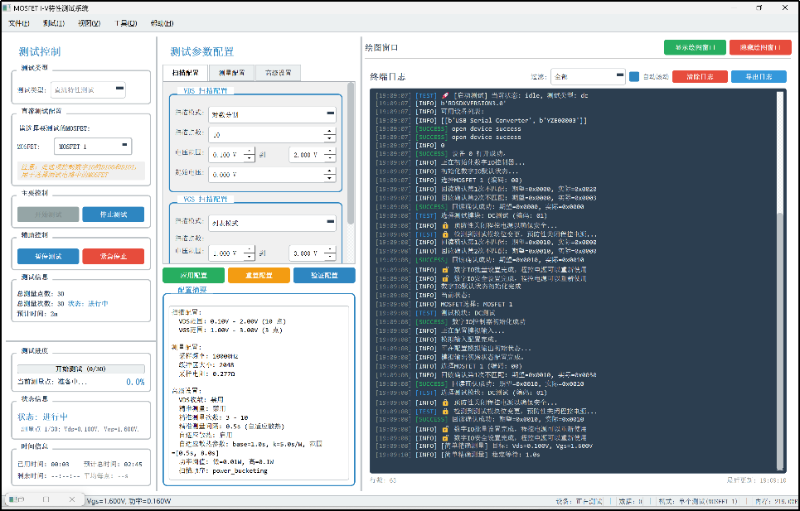

Measure软件用户界面,该软件用于控制测试平台、采集数据

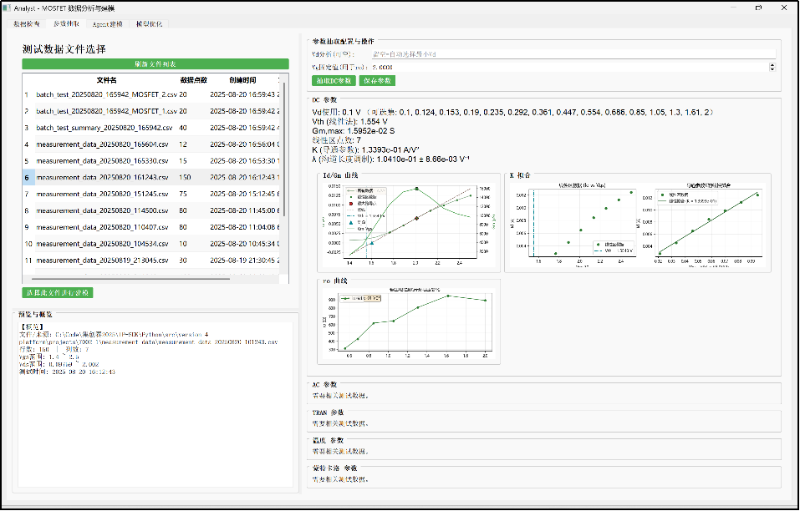

Analyst软件用户界面,该软件用于提取参数、器件建模

团队独立设计并实现了一款全新的测试负载板,为后续精准测量与控制提供了硬件基础;构建了“大模型驱动与本地迭代优化相结合”的器件建模新范式,通过“验证-优化-微调”的闭环迭代,实现了建模速度与最终精度的平衡,确保了模型的可靠性,同时提出一种基于增益预测的输出电压快速收敛算法,开发了基于多维特征监测的数据质量保障方法,设计了一种抑制器件温漂的智能测试序列规划算法。