交大要闻

交大要闻

上海交大严骏驰团队联手华为诺亚,刷新EDA逻辑综合国际权威榜单12个单项世界记录

近日,EDA逻辑综合旗舰会议IWLS2023(The International Workshop on Logic and Synthesis)公布了一年一度的比赛打榜结果,上海交通大学电子信息与电气工程学院计算机系ReThinklab实验室(导师严骏驰、硕士生袁健勇/王佩宇等)和华为诺亚(叶俊杰等)联手提出Exploration-enhanced Logic Synthesis Sequence Optimization via Reinforcement Learning (EasyRL),取得逻辑综合国际权威榜单12/40个单项第一,并刷新此12项的世界记录。

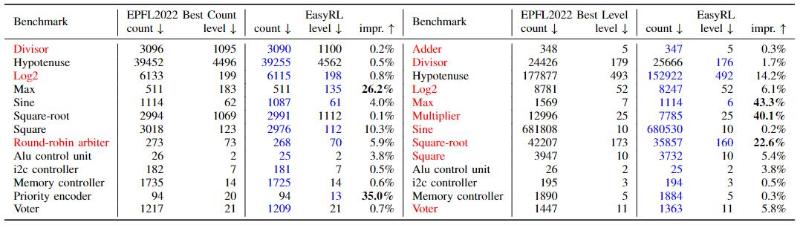

电院严骏驰教授实验室与华为诺亚的联合队伍在电子设计自动化(EDA)逻辑综合领域取得了突破性进展。他们成功克服了逻辑综合算子序列优化问题中搜索空间巨大和样本稀缺的挑战,研发了一种基于强化学习的通用黑盒优化技术EasyRL。在国际权威逻辑综合比赛EPFL Combinational Benchmark Suite2023中,该团队刷新了26/40个电路的逻辑综合结果,在多个电路上比去年最优的结果有22%~43%的进一步优化效果,并在12个单向电路中获得第一名,总排名位居所有参赛队伍前列。

交大华为联合参赛队伍所提出的EasyRL刷新26个2022年最优电路列表(蓝字部分),并在12个电路(红字部分)上取得比赛第一名

背景介绍:

逻辑综合是EDA中极为重要的一个环节,通过逻辑函数优化、电路结构调整将硬件描述语言转化为门级网表,其作用就像是编程语言中的编译器,连接着EDA芯片设计流程中的前端和后端,极大地影响着芯片性能(面积、时延和功耗)。

EPFL Combinational Benchmark Suite是一项国际权威的逻辑综合榜单,用于对比业界及学术界最优的组合电路综合、优化算法。该榜单共有20个电路,其中包含10个算术电路(Arithmetic Benchmarks)和10个控制电路(Random/Control Benchmarks)。榜单上分别记录了历年来上述20个电路(基于LUT-6)层级最优和面积最优实现,因此共计40个优化目标。在2017年至2020年的比赛中,主要由新思科技、瑞士洛桑联邦理工学院和加州大学伯克利分校等国外机构和大学在用基于专家经验的启发式方法进行头部竞争。2021年至2022年,华为作为首家国内企业参赛,提出了HIMAP、BOiLS、NAILS等基于启发式和贝叶斯优化的方法,冲破封锁,夺得了榜单的多个第一。但随后不久又被美国Rapid Silicon公司刷新多个电路,其占领了几乎整个榜单长达半年之久而无人超越。

此次上海交大严骏驰教授实验室与华为诺亚的联合队伍提出的EasyRL重新刷新了Rapid Silicon公司占榜的26个电路结果(对应层级或面积目标),并在EPFL Combinational Benchmark Suite 2023榜单上取得了12个单向电路的第一名。由于不受逻辑综合领域知识的限制,该方法也可以直接泛化到其它序列调优问题上,为EDA全流程以至于其它更广泛的领域提供了一种通用的优化方法。

参考链接:

[1] IWLS2023大会:

https://www.iwls.org/iwls2023/

[2] 2023年IWLS揭榜的逻辑综合榜单最优方案与综合效果:

https://github.com/lsils/benchmarks/tree/master/best_results

[3] 美国一家专门针对FPGA优化的公司Rapid Silicon: